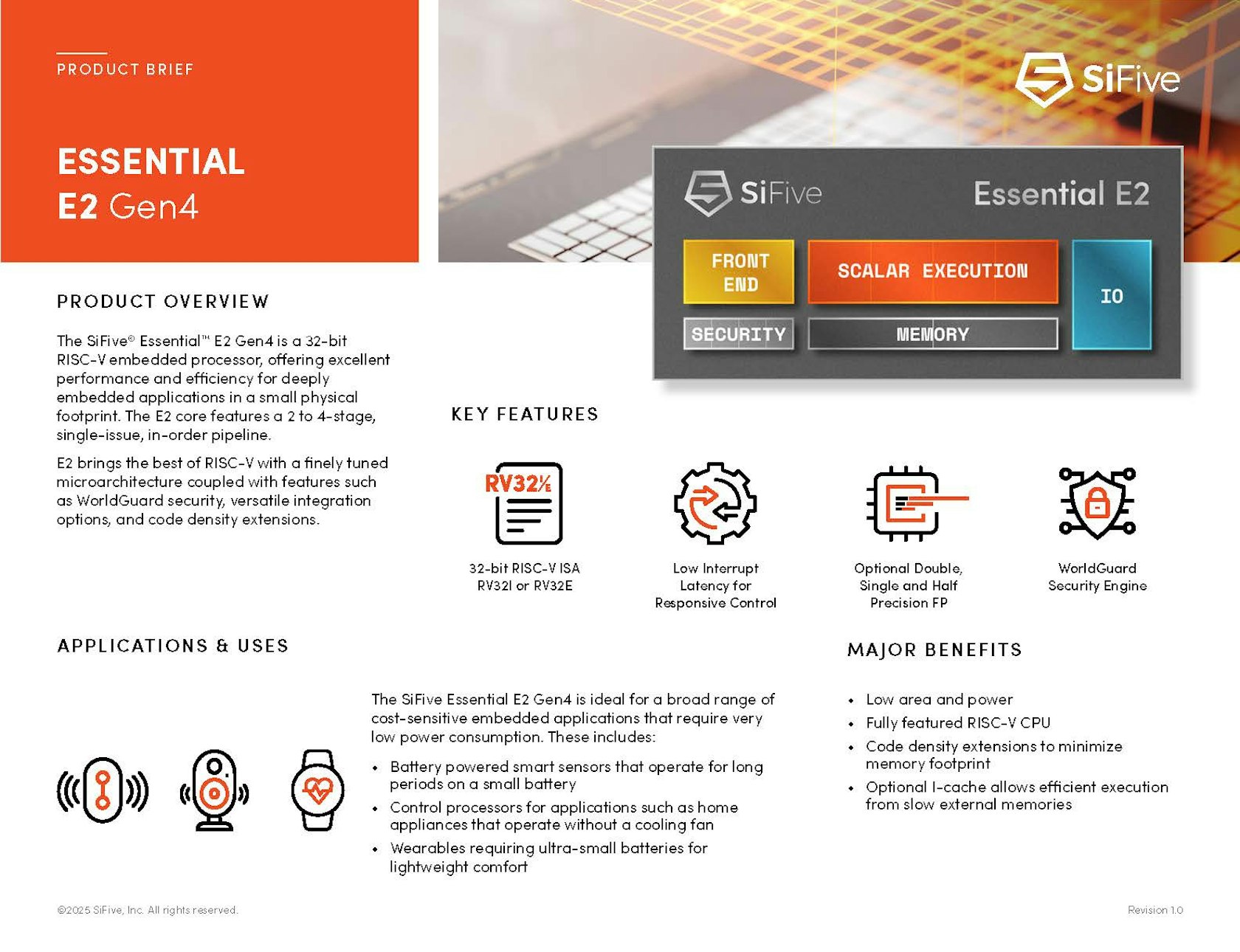

The SiFive Essential™ E Series Gen 4 are the smallest, most configurable 32-bit SiFive processors available, offering extremely efficient, optimized, low area and power solutions.

The E Series efficiently addresses traditional 8-bit and 32-bit microcontroller applications such as IoT, analog mixed signal, power management integrated circuits (PMIC) and programmable finite state machines (FSM).

- Highly configurable feature set

- Scalable performance

- 32-bit embedded

- 2-8 stage single- or dual-issue pipeline

- Power & area optimized