The SiFive Performance™ P450/470-Series application processors are SiFive’s first efficiency-focused Out-of-Order processors. The P400-series is derived from the successful and mature P500-Series, with considerable finely-tuned optimizations for best-in-class performance efficiency and compute density.

The P470 vector application processor, with a 128-bit RISC-V Vector ALU, is capable of 2x the single thread performance of an Arm Cortex-A55, achieving >8 SpecINT2k6/GHz, still within similar power budgets, representing a significant upgrade to legacy efficiency class cores currently available.

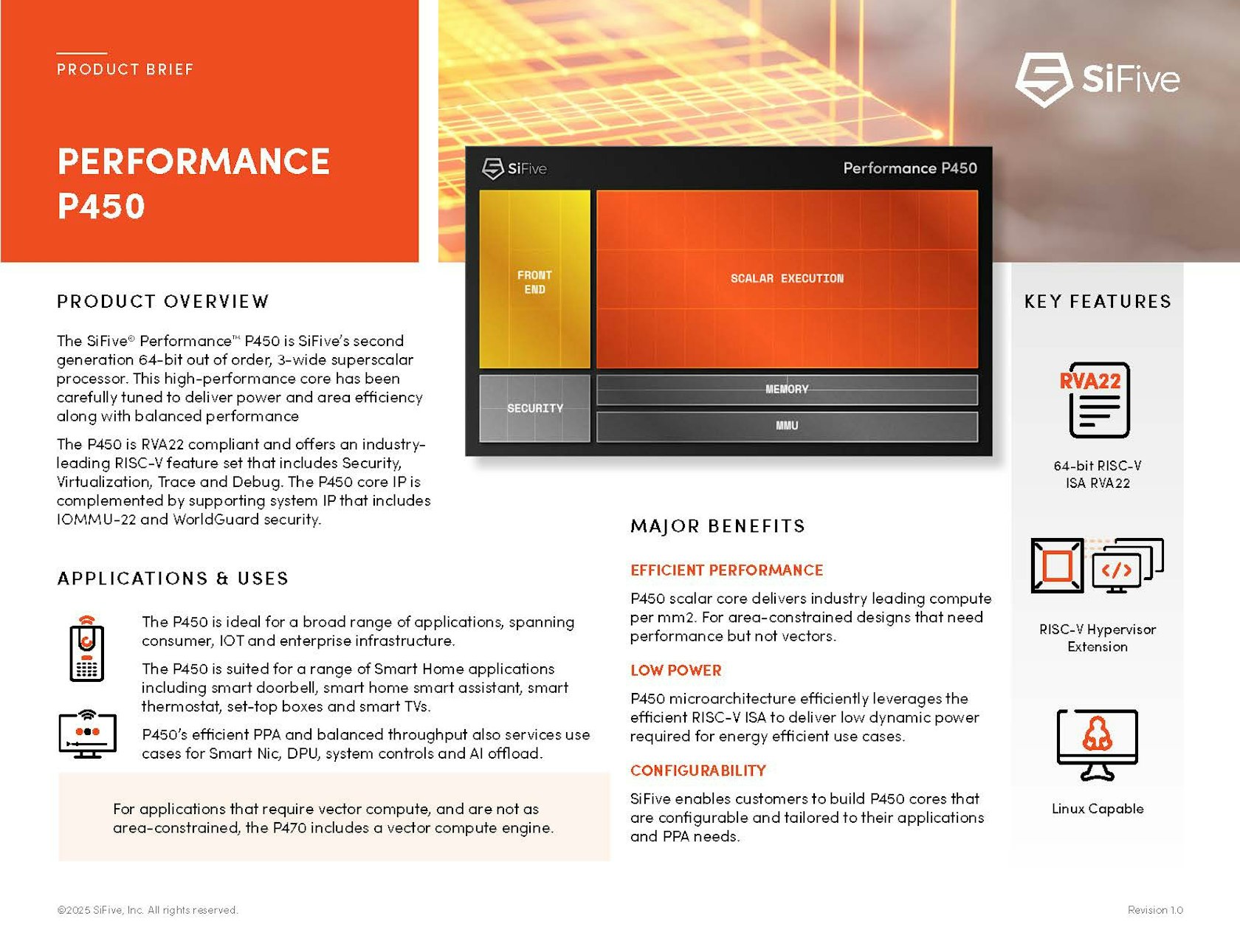

For applications that don't require vector compute, or for more area-constrained markets, the P450 offers similar performance levels in a smaller area footprint.