Webinars & Videos

View the Limitless Potential of RISC‑V

Webinars

LLM Optimization and Deployment on SiFive Intelligence

Discover how RISC-V drives cutting-edge AI/ML technology.

View More DetailsKrste Asanovic with Google's Cliff Young on The Future of AI at the AI Hardware

Krste Asanovic, SiFive Co-Founder and Chief Architect took to the stage with Cliff Young , Google TPU architect And MLPerf Co-Founder to reveal how the latest SiFive Intelligence X280 processor with the new SiFive Vector Coprocessor Interface Extension (VCIX) is being used as the AI compute host to provide flexible programming combined with the Google MXU accelerator in the datacenter.

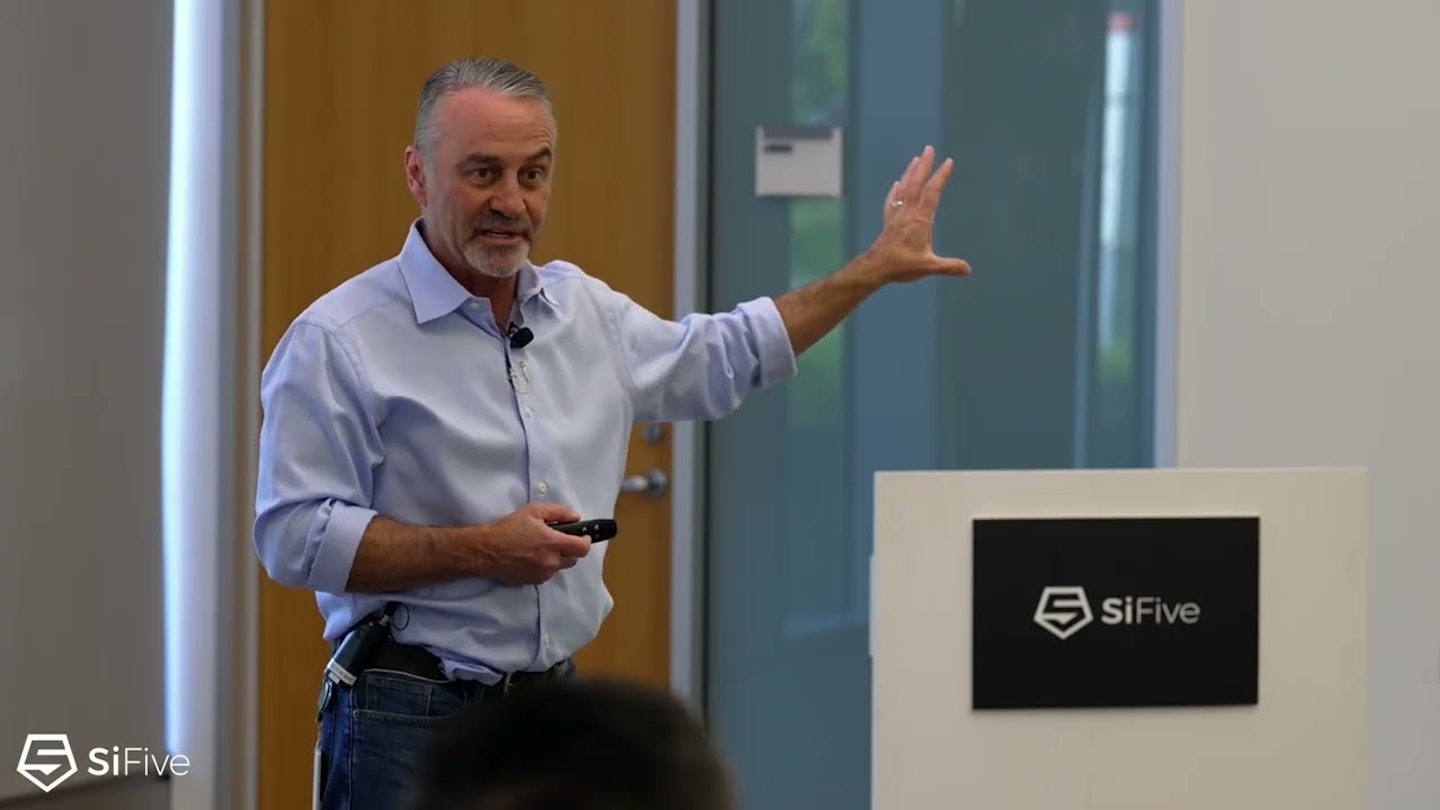

View More DetailsSiFive Performance Family of Products Webinar

The recently announced SiFive Performance family of processors is a significant milestone in SiFive’s commitment to delivering a complete, scalable portfolio of RISC-V cores. In this webinar, Drew Barbier, Senior Director of Product Marketing, will introduce the Performance P270 and P550, both available now, and how SiFive continues to set the standard in RISC-V architecture.

View More DetailsVideos

Tiling in Software for SiFive Vector-Matrix Extension (VME) - Technology Explainer

RISC-V Explained - RISC-V Extensions for AI

SiFive 2nd Generation Intelligence Technology Explainer

SiFive 2nd Generation Intelligence Family Introduction

Introducing the SiFive HiFive Premier P550

RISC-V Summit Announcement Preview

The Future of Compute

RISC-V is Built for Artificial Intelligence and SiFive Solutions for AI

SiFive Product Update

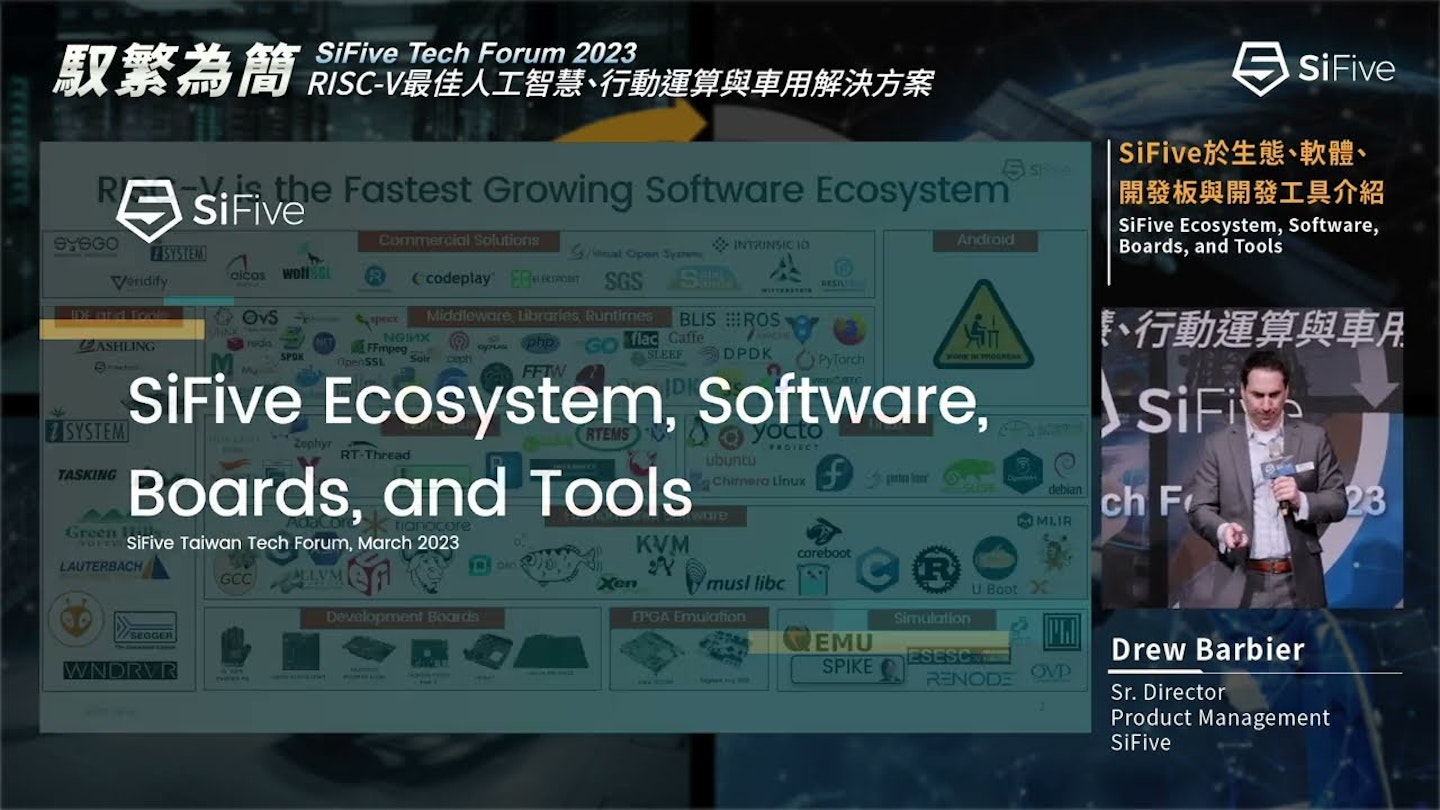

SiFive Ecosystem Software Boards and Tools

The RISC-V Revolution